# **SJA2020**

# **ARM7** microcontroller with CAN and LIN controllers

Rev. 01 — 5 April 2006

**Objective data sheet**

# 1. Introduction

# 1.1 About this document

This document lists detailed information about the SJA2020 device. It focuses on factual information like pin information, register views, characteristics etc. Short descriptions are used to outline the concept of the features and functions. More details and background on developing applications for this device is given in the SJA2020 User manual (see <u>Ref. 1</u>). No explicit references are made to the User manual.

Please refer to the SJA2020 Application note 'Known issues' (see <u>Ref. 2</u>) for corrections and additional product information.

#### **1.2 Intended audience**

This document is written for engineers evaluating and/or developing systems, hard- and/or software for the SJA2020. Some basic knowledge of ARM processors and architecture and ARM7 in particular is assumed (see <u>Ref. 3</u>).

# 2. General description

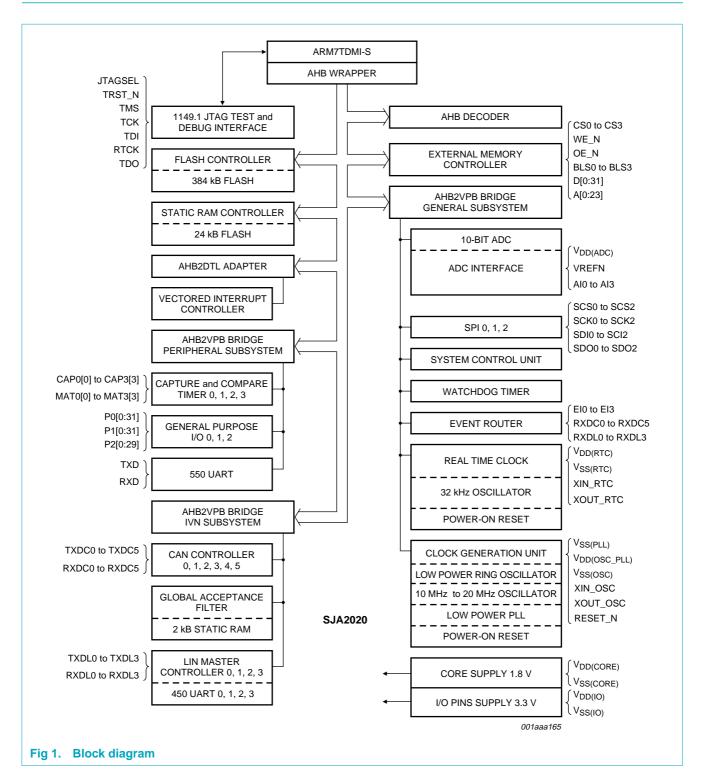

#### 2.1 Architectural overview

The SJA2020 consists of an ARM7TDMI-S processor with real-time emulation support, the AMBA Advanced High-performance Bus (AHB) for interface to the on-chip memory controllers, a DTL bus (a universal Philips interface) for interface to the interrupt controller and three VLSI Peripheral Buses (VPB - a compatible superset of ARMs AMBA advanced peripheral bus) for connection to the on-chip peripherals clustered in so-called subsystems. The SJA2020 configures the ARM7TDMI-S processor in little endian byte order. All peripherals run on the same system clock frequency as the ARM7TDMI-S processor to minimize the access latency time. The AHB2VPB bridge used in the subsystems contain a write-ahead buffer of 1 deep. This implies that when the ARM7 writes to a register located at the VPB side of the bridge, it will continue even though the actual write may not yet have taken place. Completion of a second write to the same subsystem will not be executed until the first write is finished.

# 2.2 ARM7TDMI-S processor

The ARM7TDMI-S is a general purpose 32-bit processor, which offers high performance and very low power consumption. The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers (CISC). This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective controller core.

www.DataSheet4U.com

ataSheet4U.com

Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI-S processor also employs a unique architectural strategy known as Thumb, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind Thumb is that of a super-reduced instruction set. Essentially, the ARM7TDMI-S processor has two instruction sets:

- Standard 32-bit ARM set

- 16-bit Thumb set

The Thumb set's 16-bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16-bit controller using 16-bit registers. This is possible because Thumb code operates on the same 32-bit register set as ARM code.

Thumb code is able to provide up to 65 % of the code size of ARM, and 160 % of the performance of an equivalent ARM controller connected to a 16-bit memory system.

The ARM7TDMI-S processor is described in detail in the ARM7TDMI-S data sheet (see Ref. 3).

# 2.3 On-chip flash memory system

The SJA2020 includes up to 384 kB flash memory system. This memory may be used for both code and data storage. Programming of the flash memory may be accomplished in several ways. It may be programmed in-system via a serial port, like e.g. CAN. The application program may also erase and/or program the flash while the application is running, allowing a great degree of flexibility for data storage field upgrades.

# 2.4 On-chip static RAM

The SJA2020 includes a 24 kB static RAM memory that may be used for code and/or data storage.

# 3. Features

#### 3.1 General

- ARM7TDMI-S processor at 60 MHz maximum

- Up to 384 kB on-chip flash program memory

- 24 kB static RAM

- One 550 UART with 16 bytes TX and RX FIFO depths

- Three full-duplex SPIs with 16 bits wide, 8 locations deep TX FIFO and RX FIFO

- Four 32-bit timers containing each four capture and compare registers linked to I/Os

- 10-bit, 400 ksample/s, 4-channel ADC with external trigger start option

- Real time clock with on-chip 32 kHz crystal oscillator and (battery) supply

- 32-bit watchdog with timer change protection

- 94 general purpose I/O pins with programmable pull-up

- Vectored interrupt controller with 16 priority levels

- External 8-bit, 16-bit or 32-bit bus with four memory banks

- Standard ARM test and debug interface with real-time in-circuit emulator

- Dual power supply:

- CPU operating voltage: 1.8 V ± 5 %

- I/O operating voltage: 3.3 V

- ◆ 5 V tolerant port pins (without pull-up)

- Configurable system power management

- Twelve level sensitive external interrupt pins

- Processor wake-up from power down via external interrupt pins, CAN or LIN activity

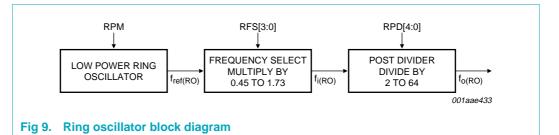

- On-chip low power ring-oscillator with operating range from 25 kHz to 1 MHz

- On-chip crystal oscillator with operating range from 10 MHz to 20 MHz

- On-chip PLL allows CPU operation up to maximum CPU rate of 60 MHz

- Automotive product qualification according AEC-Q100 Rev-F:

- Temperature grade 2 compliant; ambient operating temperature from -40 °C to +105 °C

- Boundary scan test supported

- Small 144-pin LQFP package

#### 3.2 Flash memory

- Consisting of sectors of 8 kB

- Supporting in-system and in-application programming

- Fast programming capability at 4 Mbit/s

- Provisions against over-burning and over-erasing

- Source code protection

### 3.3 CAN gateway

- Six CAN controllers

- Full CAN mode for message reception

- Triple transmit buffers with automatic priority scheduling

- Extensive global CAN acceptance filter for high performance gateway functionality

# 3.4 LIN master controller

- Four dedicated LIN master controllers

- Four standard 450 UARTs with LIN enhancement for LIN slaves or general purposes

# 4. Ordering information

| Table 1: Ordering information |         |                                                                                     |          |  |  |  |

|-------------------------------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|

| Type number                   | Package | age                                                                                 |          |  |  |  |

|                               | Name    | Description                                                                         | Version  |  |  |  |

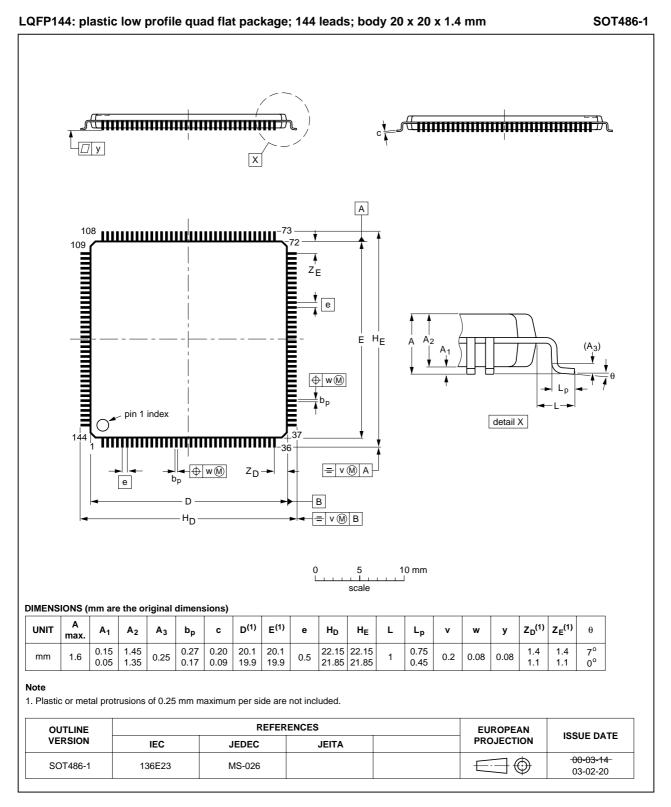

| SJA2020HL/623[1]              | LQFP144 | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |  |  |

SJA2020 1

[1] SJA2020HL/623 has 384 kB flash consisting of 48 sectors of 8 kB.

# 5. Block diagram

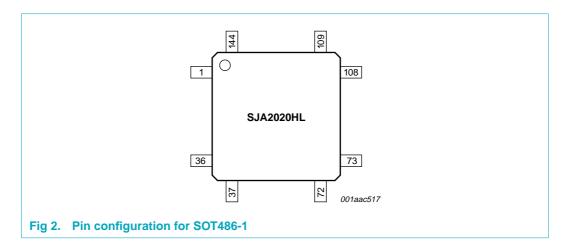

# 6. Pinning information

# 6.1 Pinning

# 6.2 Pin description

| Symbol                   | Pin | Description                                      |                                           |                  |            |  |

|--------------------------|-----|--------------------------------------------------|-------------------------------------------|------------------|------------|--|

|                          |     | Default function                                 | Function 1                                | Function 2       | Function 3 |  |

| JTAGSEL                  | 1   | TAP controller selected level selects bound      | · ·                                       |                  | 0          |  |

| RESET_N                  | 2   | external reset input                             | ; pulled-up internal                      | lly (active LOW) |            |  |

| V <sub>SS(RTC)</sub>     | 3   | real time clock osci                             | llator ground                             |                  |            |  |

| XOUT_RTC                 | 4   | real time clock crys                             | tal output                                |                  |            |  |

| XIN_RTC                  | 5   | real time clock crys                             | tal input or externa                      | I clock input    |            |  |

| V <sub>DD(RTC)</sub>     | 6   | real time clock osci                             | real time clock oscillator supply voltage |                  |            |  |

| V <sub>SS(OSC)</sub>     | 7   | oscillator ground                                |                                           |                  |            |  |

| XOUT_OSC                 | 8   | oscillator crystal output                        |                                           |                  |            |  |

| XIN_OSC                  | 9   | oscillator crystal input or external clock input |                                           |                  |            |  |

| V <sub>DD(OSC_PLL)</sub> | 10  | oscillator and PLL supply voltage                |                                           |                  |            |  |

| V <sub>SS(PLL)</sub>     | 11  | PLL ground                                       |                                           |                  |            |  |

| P0[31]/SDO0              | 12  | GPIO 0; pin 31                                   | GPIO 0; pin 31                            | SPI0 SDO         | SPI0 SDO   |  |

| P0[30]/SDI0              | 13  | GPIO 0; pin 30                                   | GPIO 0; pin 30                            | SPI0 SDI         | SPI0 SDI   |  |

| P0[29]/SCK0              | 14  | GPIO 0; pin 29                                   | GPIO 0; pin 29                            | SPI0 SCK         | SPI0 SCK   |  |

| P0[28]/SCS0              | 15  | GPIO 0; pin 28                                   | GPIO 0; pin 28                            | SPI0 SCS         | SPI0 SCS   |  |

| V <sub>SS(IO)</sub>      | 16  | I/O pins ground                                  |                                           |                  |            |  |

| P0[27]/SDO1              | 17  | GPIO 0; pin 27                                   | GPIO 0; pin 27                            | SPI1 SDO         | SPI1 SDO   |  |

| V <sub>DD(CORE)</sub>    | 18  | core supply voltage                              | e 1.8 V                                   |                  |            |  |

| V <sub>SS(CORE)</sub>    | 19  | digital core ground                              |                                           |                  |            |  |

| P0[26]/SDI1              | 20  | GPIO 0; pin 26                                   | GPIO 0; pin 26                            | SPI1 SDI         | SPI1 SDI   |  |

| P0[25]/SCK1              | 21  | GPIO 0; pin 25                                   | GPIO 0; pin 25                            | SPI1 SCK         | SPI1 SCK   |  |

SJA2020\_1

Objective data sheet

# **Philips Semiconductors**

#### **ARM7** microcontroller with CAN and LIN controllers

www.DataSheet4U.com

### Table 2: LQFP144 pin assignment ...continued

| Symbol              | Pin | Description                   |                   |             |             |

|---------------------|-----|-------------------------------|-------------------|-------------|-------------|

|                     |     | Default function              | Function 1        | Function 2  | Function 3  |

| P0[24]/SCS1         | 22  | GPIO 0; pin 24                | GPIO 0; pin 24    | SPI1 SCS    | SPI1 SCS    |

| V <sub>DD(IO)</sub> | 23  | I/O pins supply voltage 3.3 V |                   |             |             |

| P0[23]/SDO2/A[23]   | 24  | GPIO 0; pin 23                | SPI2 SDO          | EXT BUS A23 | EXT BUS A23 |

| P0[22]/SDI2/A[22]   | 25  | GPIO 0; pin 22                | SPI2 SDI          | EXT BUS A22 | EXT BUS A22 |

| P0[21]/SCK2/A[21]   | 26  | GPIO 0; pin 21                | SPI2 SCK          | EXT BUS A21 | EXT BUS A21 |

| P0[20]/SCS2/A[20]   | 26  | GPIO 0; pin 20                | SPI2 SCS          | EXT BUS A20 | EXT BUS A20 |

| V <sub>SS(IO)</sub> | 28  | I/O pins ground               |                   |             |             |

| P0[19]/A[19]        | 29  | GPIO 0; pin 19                | GPIO 0; pin 19    | EXT BUS A19 | EXT BUS A19 |

| P0[18]/A[18]        | 30  | GPIO 0; pin 18                | GPIO 0; pin 18    | EXT BUS A18 | EXT BUS A18 |

| P0[17]/A[17]        | 31  | GPIO 0; pin 17                | GPIO 0; pin 17    | EXT BUS A17 | EXT BUS A17 |

| P0[16]/A[16]        | 32  | GPIO 0; pin 16                | GPIO 0; pin 16    | EXT BUS A16 | EXT BUS A16 |

| / <sub>DD(IO)</sub> | 33  | I/O pins supply vol           | tage 3.3 V        |             |             |

| P0[15]/A[15]        | 34  | GPIO 0; pin 15                | GPIO 0; pin 15    | EXT BUS A15 | EXT BUS A15 |

| P0[14]/A[14]        | 35  | GPIO 0; pin 14                | GPIO 0; pin 14    | EXT BUS A14 | EXT BUS A14 |

| TDI                 | 36  | test data input; pul          | led-up internally |             |             |

| TDO                 | 37  | test data output              |                   |             |             |

| P0[13]/A[13]        | 38  | GPIO 0; pin 13                | GPIO 0; pin 13    | EXT BUS A13 | EXT BUS A13 |

| P0[12]/A[12]        | 39  | GPIO 0; pin 12                | GPIO 0; pin 12    | EXT BUS A12 | EXT BUS A12 |

| V <sub>SS(IO)</sub> | 40  | I/O pins ground               |                   |             |             |

| P0[11]/A[11]        | 41  | GPIO 0; pin 11                | GPIO 0; pin 11    | EXT BUS A11 | EXT BUS A11 |

| P0[10]/A[10]        | 42  | GPIO 0; pin 10                | GPIO 0; pin 10    | EXT BUS A10 | EXT BUS A10 |

| P0[9]/A[9]          | 43  | GPIO 0; pin 9                 | GPIO 0; pin 9     | EXT BUS A9  | EXT BUS A9  |

| P0[8]/A[8]          | 44  | GPIO 0; pin 8                 | GPIO 0; pin 8     | EXT BUS A8  | EXT BUS A8  |

| / <sub>DD(IO)</sub> | 45  | I/O pins supply vol           | tage 3.3 V        |             |             |

| P0[7]/A[7]          | 46  | GPIO 0; pin 7                 | GPIO 0; pin 7     | EXT BUS A7  | EXT BUS A7  |

| P0[6]/A[6]          | 47  | GPIO 0; pin 6                 | GPIO 0; pin 6     | EXT BUS A6  | EXT BUS A6  |

| P0[5]/A[5]          | 48  | GPIO 0; pin 5                 | GPIO 0; pin 5     | EXT BUS A5  | EXT BUS A5  |

| P0[4]/A[4]          | 49  | GPIO 0; pin 4                 | GPIO 0; pin 4     | EXT BUS A4  | EXT BUS A4  |

| V <sub>SS(IO)</sub> | 50  | I/O pins ground               |                   |             |             |

| P0[3]/A[3]          | 51  | GPIO 0; pin 3                 | GPIO 0; pin 3     | EXT BUS A3  | EXT BUS A3  |

| P0[2]/A[2]          | 52  | GPIO 0; pin 2                 | GPIO 0; pin 2     | EXT BUS A2  | EXT BUS A2  |

| P0[1]/A[1]          | 53  | GPIO 0; pin 1                 | GPIO 0; pin 1     | EXT BUS A1  | EXT BUS A1  |

| SS(CORE)            | 54  | digital core ground           |                   |             |             |

| DD(CORE)            | 55  | core supply voltage           | e 1.8 V           |             |             |

| P0[0]/A[0]          | 56  | GPIO 0; pin 0                 | GPIO 0; pin 0     | EXT BUS A0  | EXT BUS A0  |

| / <sub>DD(IO)</sub> | 57  | I/O pins supply vol           | tage 3.3 V        |             |             |

| P2[29]/CS0          | 58  | GPIO 2; pin 29                | GPIO 2; pin 29    | EXT BUS CS0 | EXT BUS CS0 |

| P2[28]/CS1          | 59  | GPIO 2; pin 28                | GPIO 2; pin 28    | EXT BUS CS1 | EXT BUS CS1 |

| P2[27]/EI3/CS2      | 60  | GPIO 2; pin 27                | EXTINT3           | EXT BUS CS2 | EXT BUS CS2 |

| P2[26]/EI2/CS3      | 61  | GPIO 2; pin 26                | EXTINT2           | EXT BUS CS3 | EXT BUS CS3 |

SJA2020\_1

**Objective data sheet**

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

6 of 176

www.DataSheet4U.com

# **Philips Semiconductors**

ARM7 microcontroller with CAN and LIN controllers

# Table 2: LQFP144 pin assignment ...continued

| Symbol                 | Pin | Description          |                        |                         |                                  |

|------------------------|-----|----------------------|------------------------|-------------------------|----------------------------------|

|                        |     | Default function     | Function 1             | Function 2              | Function 3                       |

| P2[25]/EI1             | 62  | GPIO 2; pin 25       | GPIO 2; pin 25         | EXTINT1                 | EXTINT1                          |

| P2[24]/EI0             | 63  | GPIO 2; pin 24       | GPIO 2; pin 24         | EXTINT0                 | EXTINT0                          |

| P2[23]/CAP1[0]/MAT1[0] | 64  | GPIO 2; pin 23       | GPIO 2; pin 23         | TIMER1 CAP0             | TIMER1 MAT0                      |

| P2[22]/CAP2[0]/MAT2[0] | 65  | GPIO 2; pin 22       | GPIO 2; pin 22         | TIMER2 CAP0             | TIMER2 MAT0                      |

| V <sub>DD(ADC)</sub>   | 66  | ADC supply voltag    | e and high reference   | ce level                |                                  |

| VREFN                  | 67  | ADC low reference    | e level                |                         |                                  |

| AI3                    | 68  | analog input for ch  | annel 3 and channe     | el 7                    |                                  |

| AI2                    | 69  | analog input for ch  | annel 2 and channe     | el 6                    |                                  |

| Al1                    | 70  | analog input for ch  | annel 1 and channe     | el 5                    |                                  |

| AIO                    | 71  | analog input for ch  | annel 0 and channe     | el 4                    |                                  |

| TRST_N                 | 72  | test reset input; pu | Illed-up internally (a | ctive LOW)              |                                  |

| V <sub>SS(IO)</sub>    | 73  | I/O pins ground      |                        |                         |                                  |

| P2[21]/RXDL0           | 74  | GPIO 2; pin 21       | GPIO 2; pin 21         | LIN0 RXDL               | LIN0 RXDL                        |

| P2[20]/TXDL0           | 75  | GPIO 2; pin 20       | GPIO 2; pin 20         | LIN0 TXDL               | LIN0 TXDL                        |

| P2[19]/RXD/RXDL1       | 76  | GPIO 2; pin 19       | UART RXD               | LIN1 RXDL               | LIN1 RXDL                        |

| P2[18]/TXD/TXDL1       | 77  | GPIO 2; pin 18       | UART TXD               | LIN1 TXDL               | LIN1 TXDL                        |

| P2[17]/RXDL2/RXDC5     | 78  | GPIO 2; pin 17       | LIN2 RXDL              | CAN5 RXDC               | CAN5 RXDC                        |

| P2[16]/TXDL2/TXDC5     | 79  | GPIO 2; pin 16       | LIN2 TXDL              | CAN5 TXDC               | CAN5 TXDC                        |

| P2[15]/RXDL3/RXDC4     | 80  | GPIO 2; pin 15       | LIN3 RXDL              | CAN4 RXDC               | CAN4 RXDC                        |

| P2[14]/TXDL3/TXDC4     | 81  | GPIO 2; pin 14       | LIN3 TXDL              | CAN4 TXDC               | CAN4 TXDC                        |

| V <sub>DD(IO)</sub>    | 82  | I/O pins supply vol  | tage 3.3 V             |                         |                                  |

| P2[13]/RXDC3           | 83  | GPIO 2; pin 13       | GPIO 2; pin 13         | CAN3 RXDC               | CAN3 RXDC                        |

| P2[12]/TXDC3           | 84  | GPIO 2; pin 12       | GPIO 2; pin 12         | CAN3 TXDC               | CAN3 TXDC                        |

| P2[11]/RXDC2           | 85  | GPIO 2; pin 11       | GPIO 2; pin 11         | CAN2 RXDC               | CAN2 RXDC                        |

| P2[10]/TXDC2           | 86  | GPIO 2; pin 10       | GPIO 2; pin 10         | CAN2 TXDC               | CAN2 TXDC                        |

| P2[9]/RXDC1            | 87  | GPIO 2; pin 9        | GPIO 2; pin 9          | CAN1 RXDC               | CAN1 RXDC                        |

| P2[8]/TXDC1            | 88  | GPIO 2; pin 8        | GPIO 2; pin 8          | CAN1 TXDC               | CAN1 TXDC                        |

| P2[7]/RXDC0            | 89  | GPIO 2; pin 7        | GPIO 2; pin 7          | CAN0 RXDC               | CAN0 RXDC                        |

| V <sub>SS(CORE)</sub>  | 90  | digital core ground  | 1                      |                         |                                  |

| V <sub>DD(CORE)</sub>  | 91  | core supply voltag   | e 1.8 V                |                         |                                  |

| P2[6]/TXDC0            | 92  | GPIO 2; pin 6        | GPIO 2; pin 6          | CAN0 TXDC               | CAN0 TXDC                        |

| V <sub>SS(IO)</sub>    | 93  | I/O pins ground      |                        |                         |                                  |

| P2[5]/BLS3             | 94  | GPIO 2; pin 5        | GPIO 2; pin 5          | EXT BUS BLS3            | EXT BUS BLS                      |

| P2[4]/BLS2             | 95  | GPIO 2; pin 4        | GPIO 2; pin 4          | EXT BUS BLS2            | EXT BUS BLS                      |

| P2[3]/BLS1             | 96  | GPIO 2; pin 3        | GPIO 2; pin 3          | EXT BUS BLS1            | EXT BUS BLS                      |

| P2[2]/BLS0             | 97  | GPIO 2; pin 2        | GPIO 2; pin 2          | EXT BUS BLS0            | EXT BUS BLS                      |

| P2[1]/WE_N             | 98  | GPIO 2; pin 1        | GPIO 2; pin 1          | EXT BUS WEN             | EXT BUS WEN                      |

| P2[0]/OE_N             | 99  | GPIO 2; pin 0        | GPIO 2; pin 0          | EXT BUS OEN             | EXT BUS OEN                      |

| V <sub>DD(IO)</sub>    | 100 | I/O pins supply vol  | tage 3.3 V             |                         |                                  |

| P1[0]/D[0]             | 101 | GPIO 1; pin 0        | GPIO 1; pin 0          | EXT BUS D0              | EXT BUS D0                       |

|                        |     | ,                    | ,                      |                         |                                  |

| SJA2020_1              |     | Day Of 5             |                        | © Koninklijke Philips E | lectronics N.V. 2006. All rights |

Objective data sheet

www.DataSheet4U.com

# **Philips Semiconductors**

#### **ARM7** microcontroller with CAN and LIN controllers

www.DataSheet4U.com

| Symbol                       | Pin | Description         |                      |             |             |

|------------------------------|-----|---------------------|----------------------|-------------|-------------|

|                              |     | Default function    | Function 1           | Function 2  | Function 3  |

| P1[1]/D[1]                   | 102 | GPIO 1; pin 1       | GPIO 1; pin 1        | EXT BUS D1  | EXT BUS D1  |

| P1[2]/D[2]                   | 103 | GPIO 1; pin 2       | GPIO 1; pin 2        | EXT BUS D2  | EXT BUS D2  |

| P1[3]/D[3]                   | 104 | GPIO 1; pin 3       | GPIO 1; pin 3        | EXT BUS D3  | EXT BUS D3  |

| V <sub>SS(IO)</sub>          | 105 | I/O pins ground     |                      |             |             |

| P1[4]/D[4]                   | 106 | GPIO 1; pin 4       | GPIO 1; pin 4        | EXT BUS D4  | EXT BUS D4  |

| P1[5]/D[5]                   | 107 | GPIO 1; pin 5       | GPIO 1; pin 5        | EXT BUS D5  | EXT BUS D5  |

| TMS                          | 108 | test mode select in | put; pulled-up inter | nally       |             |

| ТСК                          | 109 | test clock input    |                      |             |             |

| P1[6]/D[6]                   | 110 | GPIO 1; pin 6       | GPIO 1; pin 6        | EXT BUS D6  | EXT BUS D6  |

| P1[7]/D[7]                   | 111 | GPIO 1; pin 7       | GPIO 1; pin 7        | EXT BUS D7  | EXT BUS D7  |

| V <sub>DD(IO)</sub>          | 112 | I/O pins supply vol | tage 3.3 V           |             |             |

| P1[8]/D[8]                   | 113 | GPIO 1; pin 8       | GPIO 1; pin 8        | EXT BUS D8  | EXT BUS D8  |

| P1[9]/D[9]                   | 114 | GPIO 1; pin 9       | GPIO 1; pin 9        | EXT BUS D9  | EXT BUS D9  |

| P1[10]/D[10]                 | 115 | GPIO 1; pin 10      | GPIO 1; pin 10       | EXT BUS D10 | EXT BUS D10 |

| P1[11]/D[11]                 | 116 | GPIO 1; pin 11      | GPIO 1; pin 11       | EXT BUS D11 | EXT BUS D11 |

| V <sub>SS(IO)</sub>          | 117 | I/O pins ground     |                      |             |             |

| P1[12]/D[12]                 | 118 | GPIO 1; pin 12      | GPIO 1; pin 12       | EXT BUS D12 | EXT BUS D12 |

| P1[13]/D[13]                 | 119 | GPIO 1; pin 13      | GPIO 1; pin 13       | EXT BUS D13 | EXT BUS D13 |

| P1[14]/D[14]                 | 120 | GPIO 1; pin 14      | GPIO 1; pin 14       | EXT BUS D14 | EXT BUS D14 |

| P1[15]/D[15]                 | 121 | GPIO 1; pin 15      | GPIO 1; pin 15       | EXT BUS D15 | EXT BUS D15 |

| V <sub>DD(IO)</sub>          | 122 | I/O pins supply vol | tage 3.3 V           |             |             |

| P1[16]/CAP3[3]/D[16]/MAT3[3] | 123 | GPIO 1; pin 16      | TIMER3 CAP3          | EXT BUS D16 | TIMER3 MAT3 |

| P1[17]/CAP3[2]/D[17]/MAT3[2] | 124 | GPIO 1; pin 17      | TIMER3 CAP2          | EXT BUS D17 | TIMER3 MAT2 |

| P1[18]/CAP3[1]/D[18]/MAT3[1] | 125 | GPIO 1; pin 18      | TIMER3 CAP1          | EXT BUS D18 | TIMER3 MAT1 |

| V <sub>DD(CORE)</sub>        | 126 | core supply voltage | e 1.8 V              |             |             |

| V <sub>SS(CORE)</sub>        | 127 | digital core ground |                      |             |             |

| P1[19]/CAP3[0]/D[19]/MAT3[0] | 128 | GPIO 1; pin 19      | TIMER3 CAP0          | EXT BUS D19 | TIMER3 MATO |

| V <sub>SS(IO)</sub>          | 129 | I/O pins ground     |                      |             |             |

| P1[20]/CAP2[3]/D[20]/MAT2[3] | 130 | GPIO 1; pin 20      | TIMER2 CAP3          | EXT BUS D20 | TIMER2 MAT3 |

| P1[21]/CAP2[2]/D[21]/MAT2[2] | 131 | GPIO 1; pin 21      | TIMER2 CAP2          | EXT BUS D21 | TIMER2 MAT2 |

| P1[22]/CAP2[1]/D[22]/MAT2[1] | 132 | GPIO 1; pin 22      | TIMER2 CAP1          | EXT BUS D22 | TIMER2 MAT1 |

| P1[23]/CAP1[3]/D[23]/MAT1[3] | 133 | GPIO 1; pin 23      | TIMER1 CAP3          | EXT BUS D23 | TIMER1 MAT3 |

| V <sub>DD(IO)</sub>          | 134 | I/O pins supply vol | tage 3.3 V           |             |             |

| P1[24]/CAP1[2]/D[24]/MAT1[2] | 134 | GPIO 1; pin 24      | TIMER1 CAP2          | EXT BUS D24 | TIMER1 MAT2 |

| P1[25]/CAP1[1]/D[25]/MAT1[1] | 136 | GPIO 1; pin 25      | TIMER1 CAP1          | EXT BUS D25 | TIMER1 MAT1 |

| P1[26]/CAP0[3]/D[26]/MAT0[3] | 137 | GPIO 1; pin 26      | TIMER0 CAP3          | EXT BUS D26 | TIMER0 MAT3 |

| P1[27]/CAP0[2]/D[27]/MAT0[2] | 138 | GPIO 1; pin 27      | TIMER0 CAP2          | EXT BUS D27 | TIMER0 MAT2 |

| V <sub>SS(IO)</sub>          | 139 | I/O pins ground     |                      |             |             |

| P1[28]/CAP0[1]/D[28]/MAT0[1] | 140 | GPIO 1; pin 28      | TIMER0 CAP1          | EXT BUS D28 | TIMER0 MAT1 |

| P1[29]/CAP0[0]/D[29]/MAT0[0] | 141 | GPIO 1; pin 29      | TIMER0 CAP0          | EXT BUS D29 | TIMER0 MATO |

#### Table 2: LQFP144 pin assignment ...continued

SJA2020\_1

| Table 2:            | LQFP144 pin assignmentcontinued |     |                               |                |             |             |

|---------------------|---------------------------------|-----|-------------------------------|----------------|-------------|-------------|

| Symbol              |                                 | Pin | Description                   |                |             |             |

|                     |                                 |     | Default function              | Function 1     | Function 2  | Function 3  |

| P1[30]/RT           | CK/D[30]                        | 142 | GPIO 1; pin 30                | RTCK           | EXT BUS D30 | EXT BUS D30 |

| P1[31]/D[3          | 31]                             | 143 | GPIO 1; pin 31                | GPIO 1; pin 31 | EXT BUS D31 | EXT BUS D31 |

| V <sub>DD(IO)</sub> |                                 | 144 | I/O pins supply voltage 3.3 V |                |             |             |

# 7. Functional description

# 7.1 Reset and power-up behavior

The SJA2020 contains an external reset input and an internal power-up reset circuitry. This circuitry ensures a reset is internally extended until oscillators, PLL and Flash have reached a stable state. See <u>Section 12</u> for characteristics of the several start-up and initialization times. <u>Table 3</u> shows the reset pin.

| Table 3: | Reset pin |                                                        |

|----------|-----------|--------------------------------------------------------|

| Symbol   | Direction | Description                                            |

| RESET_N  | IN        | external reset input, active LOW; pulled-up internally |

# 7.2 JTAG interface and debug pins

The SJA2020 contains boundary scan test logic according to IEEE 1149.1, in this document further referred to as 'JTAG'. The JTAG pins can be used to connect a debugger probe for the embedded ARM processor. Pin JTAGSEL selects between the boundary scan mode and debug mode. See User manual for more information (see Ref. 1). Table 4 shows the JTAG pins.

#### Table 4: JTAG and debug interface

| Symbol  | Direction | Description                                                                                                                                    |  |  |  |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAGSEL | IN        | TAP controller select input; LOW level selects ARM debug mode and HIGH level selects boundary scan and flash programming; pulled-up internally |  |  |  |

| TRST_N  | IN        | test reset input; pulled-up internally (active LOW)                                                                                            |  |  |  |

| TMS     | IN        | test mode select input; pulled-up internally                                                                                                   |  |  |  |

| TDI     | IN        | test data input, pulled-up internally                                                                                                          |  |  |  |

| TDO     | OUT       | test data output                                                                                                                               |  |  |  |

| тск     | IN        | test clock input                                                                                                                               |  |  |  |

| RTCK    | OUT       | synchronized ARM debug return clock output (multiplexed with other functions on a device pin, see Section 6)                                   |  |  |  |

# 7.3 Power supply pins description

<u>Table 5</u> shows the power supply pins. See User manual (see <u>Ref. 1</u>) for more information on physical constraints and board design issues.

| Table 5: Pov          | ver supplies                                    |

|-----------------------|-------------------------------------------------|

| Symbol                | Description                                     |

| V <sub>DD(CORE)</sub> | core supply voltage 1.8 V                       |

| V <sub>SS(CORE)</sub> | core ground                                     |

| V <sub>DD(IO)</sub>   | I/O supply voltage 3.3 V                        |

| V <sub>SS(IO)</sub>   | I/O ground                                      |

| $V_{DD(OSC\_PLL)}$    | oscillator and PLL supply voltage 1.8 V         |

| V <sub>SS(OSC)</sub>  | oscillator ground                               |

| V <sub>DD(RTC)</sub>  | real time clock oscillator supply voltage 1.8 V |

| V <sub>SS(RTC)</sub>  | real time clock oscillator ground               |

| V <sub>DD(ADC)</sub>  | ADC supply voltage 3.3 V                        |

| V <sub>SS(PLL)</sub>  | PLL ground                                      |

# 7.4 Clock architecture

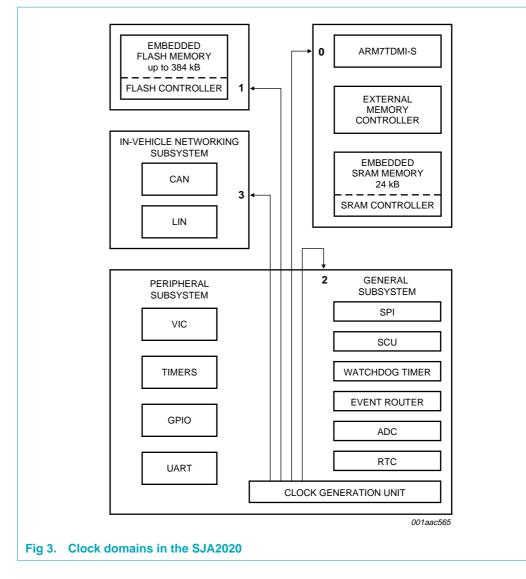

As can be seen in Figure 3, the SJA2020 is partitioned into so called subsystems or blocks. The subsystems concept allows the several functional parts to be configured individually with respect to the power mode that is used in each of them. Subsystems and or blocks are grouped into 'clock-domains'. In this way clocks can be switched on or off and the response to sleep/wake-up events can be set per clock domain. In Section 8.3.1 these features are described in more detail.

Figure 3 gives a simplified view of how the SJA2020 is split into several 'clock-domains'.

# 7.5 Memory maps

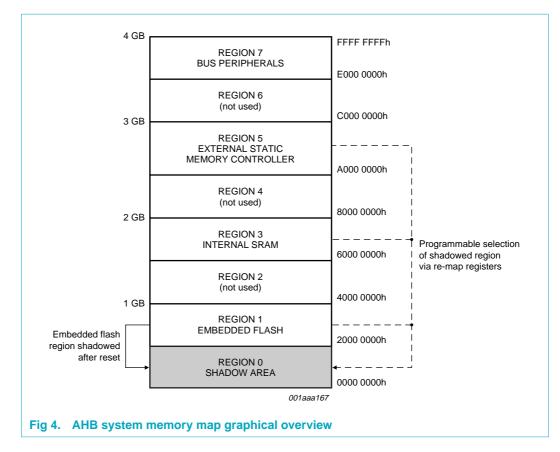

ARM7 processors have 4 GB address space. The SJA2020 has divided this memory space into 8 regions of 512 MB each. Each region is used for a dedicated purpose.

An exception to this is region 0; several of the other regions (or a part of it) can be shadowed in the memory map at this region. This shadowing can be controlled by software via the programmable re-mapping registers.

Figure 4 gives a graphical overview of the SJA2020 memory map.

### 7.5.1 Region 0: remap area

The ARM7TDMI-S processor has its exception vectors located at address logic 0. Since flash is the only non-volatile memory available in the SJA2020, the exception vectors in the flash must be located at address logic 0 after reset. Memory re-mapping from flash to SRAM is therefore introduced to improve performance.

To enable memory re-mapping, the SJA2020 AHB system memory map provides a shadow area (region 0) starting at address logic 0. This is a virtual memory region, i.e. no actual memory is present at the shadow area addresses. A selectable region of the AHB system memory map is, apart from its own specific region, also accessible via this shadow area region.

After reset, the region 1 embedded flash area is always available at the shadow area. After booting, any other region of the AHB system memory map (e.g. internal SRAM) can be re-mapped to region 0 by means of the shadow memory mapping register. For more details about the shadow area see Section 8.3.2.4.

#### 7.5.2 Region 1: embedded flash area

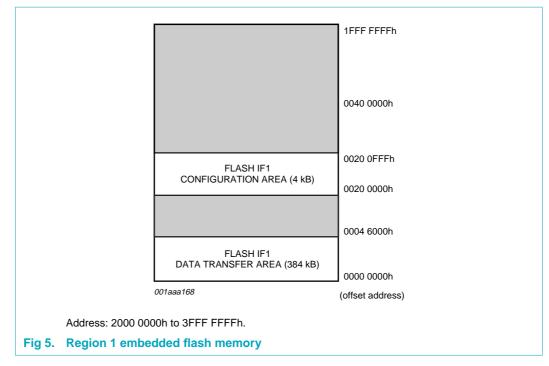

Figure 5 gives a graphical overview of the embedded flash memory map.

Region 1 is reserved for the embedded flash. For each embedded flash instance a data area of 2 MB (to be prepared for larger flash memory instance) and a configuration area of 4 kB are reserved. Although the SJA2020 contains only one embedded flash instance, the memory aperture per embedded flash instance is defined at 4 MB.

# 7.5.3 Region 2: not used

# 7.5.4 Region 3: internal SRAM area

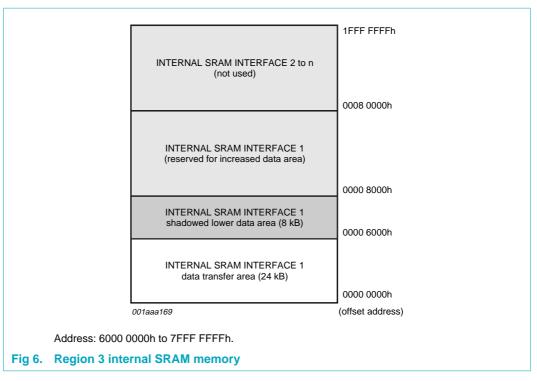

Figure 6 gives a graphical overview of the internal SRAM memory map.

Region 3 is reserved for internal SRAM. For each internal SRAM instance a data area of 512 kB is reserved. Although the SJA2020 has only one internal SRAM instance, the memory aperture per internal SRAM instance is defined at 512 kB.

# 7.5.5 Region 4: not used

# 7.5.6 Region 5: static memory controller area

|                                          | CONFIGURATION AREA (4 kB)        | 1FFF FFFFh       |  |  |  |  |  |

|------------------------------------------|----------------------------------|------------------|--|--|--|--|--|

|                                          |                                  | 1FFF F000h       |  |  |  |  |  |

|                                          | MEMORY BANK 4 to 7<br>(not used) |                  |  |  |  |  |  |

|                                          |                                  | 1000 0000h       |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 3 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 3 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 3 (16 MB)     | 0D00 0000h       |  |  |  |  |  |

|                                          | MEMORY BANK 3 (16 MB)            | 0C00 0000h       |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 2 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 2 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 2 (16 MB)     | 0900 0000h       |  |  |  |  |  |

|                                          | MEMORY BANK 2 (16 MB)            | 0800 0000h       |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 1 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 1 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 1 (16 MB)     | 0500 0000h       |  |  |  |  |  |

|                                          | MEMORY BANK 1 (16 MB)            | 0400 0000h       |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 0 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 0 (16 MB)     |                  |  |  |  |  |  |

|                                          | SHADOW MEMORY BANK 0 (16 MB)     | 0100 0000h       |  |  |  |  |  |

|                                          | MEMORY BANK 0 (16 MB)            | 0000 0000h       |  |  |  |  |  |

|                                          | 001aaa170                        | (offset address) |  |  |  |  |  |

| Address: A000 0000h to BFFF FFFFh.       |                                  |                  |  |  |  |  |  |

| Fig 7. Region 5 static memory controller |                                  |                  |  |  |  |  |  |

Figure 7 gives a graphical overview of the static memory controller memory map.

Region 5 is reserved for the static memory controller. The SJA2020 provides I/O pins for 4 bank select signals and 24 address lines. This implies that 4 memory banks of 16 MB each can be externally addressed. Due to the static memory controller hardware configuration, each bank of 16 MB data area is mirrored four times in a 64 MB region memory map.

The static memory controller configuration area is located on top of region 5.

#### 7.5.7 Region 6: not used

#### 7.5.8 Region 7: bus peripherals area

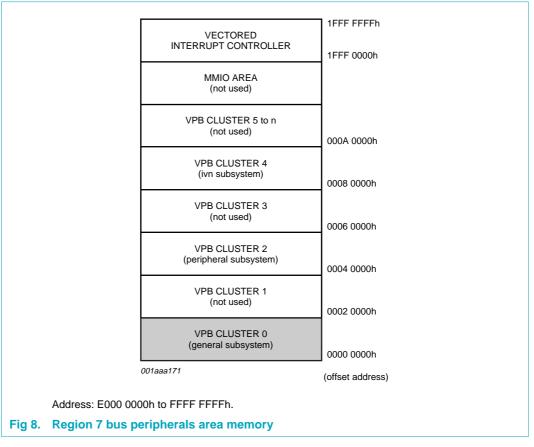

Figure 8 gives a graphical overview of the bus peripherals area memory map.

Region 7 is reserved for all 'stand-alone' memory mapped register interfaces. Examples of such peripherals are DTL target modules connected to the AHB bus via AHB2DTL adapters and VPB peripherals connected via AHB2VPB bridges.

The lower part of region 7 is again divided into VPB clusters. A VPB cluster is typically used as the address space for a set of VPB peripherals connected to a single AHB2VPB bridge, the slave on the AHB system bus. The clusters are aligned on 128 kB boundaries. In the SJA2020 three VPB clusters are in use. The VPB peripherals are aligned on 4 kB boundaries inside the VPB clusters.

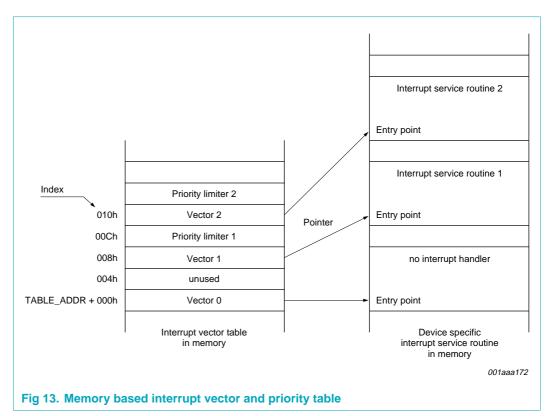

The upper part of region 7 is used as the memory area where memory mapped register interfaces of 'stand-alone' AHB peripherals reside. Each of these peripherals will be a slave on the AHB system bus. In the SJA2020 only one of such slave is present: the interrupt controller. It is a DTL target connected to the AHB system bus via an AHB2DTL adapter.

#### 7.5.9 Memory map concepts operation

The basic concept on the SJA2020 is that each memory area has a 'natural' location in the memory map. This is the address range for which code residing in that area is written. Each memory space remains permanently fixed in the same location, eliminating the need to have portions of the code designed to run in different address ranges.

Because of the location of the interrupt vectors on the ARM7 processor (at addresses 0000 0000h through 0000 001Ch) (see <u>Table 6</u>), the embedded flash, internal SRAM or even external memories can be re-mapped to the shadow memory area in order to allow alternative uses of interrupts in the different operating modes. After reset, the embedded flash is re-mapped into the shadow memory area by default.

The SJA2020 generates the appropriate bus cycle abort exception if an access is attempted for an address that is in a reserved or not used address region and unassigned peripheral spaces. For these areas, both attempted data access and instruction fetch generate an exception. Note that write access address should be word aligned in ARM code or halfword aligned in Thumb code. Byte aligned writes are performed as word or halfword aligned writes without error signalling.

Within the address space of an existing peripheral, a data abort exception is not generated in response to an access to an undefined address. Address decoding within each peripheral is limited to that needed to distinguish defined registers within the peripheral itself. Details of address aliasing within a peripheral space are not defined in the SJA2020 documentation and are not a supported feature.

Note that the ARM stores the prefetch abort flag along with the associated instruction (which will be meaningless) in the pipeline and processes the abort only if an attempt is made to execute the instruction fetched from the illegal address. This prevents accidental aborts that could be caused by prefetches that occur when code is executed very near a memory boundary.

Table 7 gives the base address overview of all peripherals.

| Table 0. Inter | Tupi vectors address table                      |

|----------------|-------------------------------------------------|

| Address        | Exception                                       |

| 0000 0000h     | reset                                           |

| 0000 0004h     | undefined instruction                           |

| 0000 0008h     | software interrupt                              |

| 0000 000Ch     | prefetch abort (instruction fetch memory fault) |

| 0000 0010h     | data abort (data access memory fault)           |

| 0000 0014h     | reserved                                        |

| 0000 0018h     | IRQ                                             |

| 0000 001Ch     | FIQ                                             |

|                |                                                 |

#### Table 6: Interrupt vectors address table

# www.DataSheet4U.com

# ARM7 microcontroller with CAN and LIN controllers

| Base address            | Base name               | AHB peripherals                                      |

|-------------------------|-------------------------|------------------------------------------------------|

| Memory region 0 to 6    |                         |                                                      |

| 0000 0000h              |                         | shadow area memory                                   |

| 2000 0000h              |                         | embedded flash memory                                |

| 2020 0000h              | FMC RegBase             | embedded flash controller<br>configuration registers |

| 6000 0000h              |                         | internal SRAM memory                                 |

| A000 0000h              |                         | external static memory                               |

| BFFF F000h              | SMC RegBase             | static memory controller<br>configuration registers  |

| VPB cluster 0: general  | subsystem               |                                                      |

| E000 0000h              | CGU RegBase             | clock generation unit                                |

| E000 1000h              | SCU RegBase             | system control unit                                  |

| E000 2000h              | SPI RegBase             | SPI 0                                                |

| E000 3000h              | SPI RegBase             | SPI 1                                                |

| E000 4000h              | SPI RegBase             | SPI 2                                                |

| E000 5000h              | ADC RegBase             | ADC                                                  |

| E000 6000h              | WD RegBase              | watchdog                                             |

| E000 8000h              | ER RegBase              | event router                                         |

| E000 A000h              | RTC RegBase             | real time clock                                      |

| VPB cluster 2: periphe  | ral subsystem           |                                                      |

| E004 0000h              | TIMER RegBase           | timer 0                                              |

| E004 1000h              | TIMER RegBase           | timer 1                                              |

| E004 2000h              | TIMER RegBase           | timer 2                                              |

| E004 3000h              | TIMER RegBase           | timer 3                                              |

| E004 4000h              | UART RegBase            | 16C550 UART                                          |

| E004 5000h              | GPIO RegBase            | general purpose I/O 0                                |

| E004 6000h              | GPIO RegBase            | general purpose I/O 1                                |

| E004 7000h              | GPIO RegBase            | general purpose I/O 2                                |

| VPB cluster 4: in-vehic | le networking subsystem |                                                      |

| E008 0000h              | CANC RegBase            | CAN controller 0                                     |

| E008 1000h              | CANC RegBase            | CAN controller 1                                     |

| E008 2000h              | CANC RegBase            | CAN controller 2                                     |

| E008 3000h              | CANC RegBase            | CAN controller 3                                     |

| E008 4000h              | CANC RegBase            | CAN controller 4                                     |

| E008 5000h              | CANC RegBase            | CAN controller 5                                     |

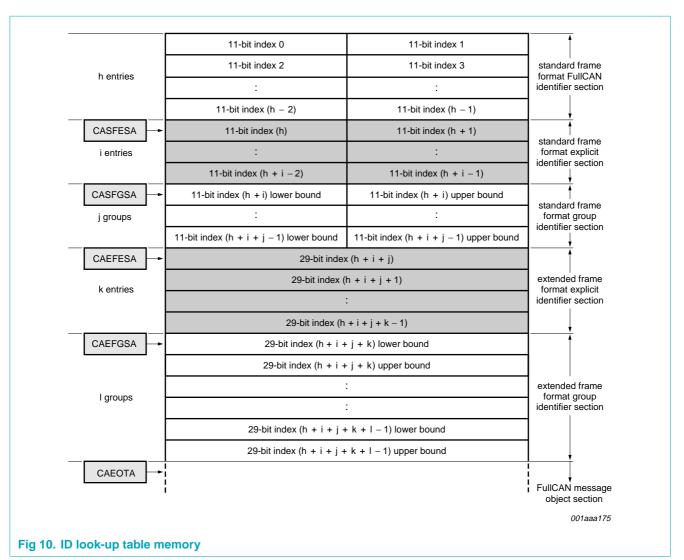

| E008 6000h              | CANAFM RegBase          | CAN ID-look-up table memory                          |

| E008 7000h              | CANAFR RegBase          | CAN acceptance filter register                       |

| E008 8000h              | CANCS RegBase           | CAN central status registers                         |

| E008 9000h              | LIN RegBase             | LIN master controller 0                              |

| E008 A000h              | LIN RegBase             | LIN master controller 1                              |

| E008 B000h              | LIN RegBase             | LIN master controller 2                              |

|                         |                         |                                                      |

#### Table 7: Peripherals base address overview

SJA2020\_1

Objective data sheet

| Table 7:         Peripherals base address overviewcontinued |             |                               |  |  |  |  |

|-------------------------------------------------------------|-------------|-------------------------------|--|--|--|--|

| Base address                                                | Base name   | AHB peripherals               |  |  |  |  |

| E008 C000h                                                  | LIN RegBase | LIN master controller 3       |  |  |  |  |

| Vector interrupt controller                                 |             |                               |  |  |  |  |

| FFFF F000h                                                  | VIC RegBase | vectored interrupt controller |  |  |  |  |

# 8. Block description

#### 8.1 Flash memory controller

#### 8.1.1 Overview

The Flash Memory Controller (FMC) interfaces to the embedded flash memory with two tasks:

- Providing memory data transfer

- Memory configuration via triggering, programming and erasing

The flash memory has a 128-bit wide data interface and the flash controller offers two 128-bit buffer lines to improve the system performance. Initially, the flash has to be programmed via JTAG. In-system programming must be supported by the boot loader. In-application programming is possible. The flash memory contents can be protected by disabling the JTAG access. Suspending of burning or erasing is not supported.

The key features are:

- Programming by CPU via AHB

- Programming by external programmer via JTAG

- JTAG access protection

- · Burn-finished and erased-finished interrupt

After reset, the flash initialization is started which takes t<sub>init</sub> time. During this initialization flash access is not possible and AHB transfers to the flash are stalled, thus blocking the AHB bus.

During the flash initialization, the index sector is read to identify the status of the JTAG access protection and sector security. In case the JTAG access protection is active, the flash is not accessible via JTAG anymore and the ARM debug facilities have been disabled to protect the flash memory contents against unwanted reading out externally. If the sector security is active, the concerning sector is read only.

The flash can be read synchronously or asynchronously to the system clock. In synchronous operation, the flash goes into standby after returning the read data. Started reads cannot be stopped and therefore speculative reading and dual buffering is not supported.

With asynchronous reading, the transfer of the address to the flash, and read data from the flash are done asynchronously, yielding in the fastest possible response time. Started reads can be stopped and therefore speculative reading and dual buffering is supported.

Buffering is offered because the flash has a 128-bit wide data interface, while the AHB interface has only 32 bits. With buffering, a buffer line holds the complete 128 bits flash word, from which 4 words can be read. Without buffering, every AHB data port read starts a flash read. A flash read is a slow process compared to the minimum AHB cycle time. With buffering, the average read time is reduced which can improve the system performance.

With single buffering, the most recently read flash word stays available until the next flash read. When an AHB data port read transfer requires data from the same flash word as the previous read transfer, no new flash read is done, and the read data is given without wait cycles.

When an AHB data port read transfer requires data from a different flash word as the previous read transfer, a new flash read is done, and wait states are given until the new read data is available.

With dual buffering, a secondary buffer line is used. The output of the flash is considered as the primary buffer. On a primary buffer hit, data can be copied to the secondary buffer line, which allows the flash to start a speculative read of the next flash word.

Both buffer lines are invalidated after:

- Initialization

- Configuration register access

- Data latch reading

- Index sector reading

The modes of operation are listed in Table 8.

#### Table 8: Flash read modes

| Buffering                                  | Config     | uration bit         |              |                 | Characteristics and features                                                                                                                                       |  |  |

|--------------------------------------------|------------|---------------------|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                            | FS_<br>DCR | FS_<br>CACHE<br>BYP | CACHE2<br>EN | Special<br>ways |                                                                                                                                                                    |  |  |

| Synchronous timing                         |            |                     |              |                 |                                                                                                                                                                    |  |  |

| No buffer line                             | 0          | 1                   | Х            | Х               | for single (non linear) reads, one flash<br>word read per word read                                                                                                |  |  |

| Single buffer<br>line                      | 0          | 0                   | Х            | Х               | default mode of operation; most<br>recently read flash word is kept until<br>another flash word is required                                                        |  |  |

| Asynchronous                               | s timing   |                     |              |                 |                                                                                                                                                                    |  |  |

| No buffer line                             | 1          | 1                   | Х            | Х               | one flash word read per word read                                                                                                                                  |  |  |

| Single buffer<br>line                      | 1          | 0                   | 0            | Х               | most recently read flash word is kept<br>until another flash word is required                                                                                      |  |  |

| Dual buffer<br>line, single<br>speculative | 1          | 0                   | 1            | 0               | on a buffer miss, a flash read is done,<br>followed by at most one speculative<br>read; optimized for execution of code<br>with small loops (< 8 words) from flash |  |  |

| Dual buffer<br>line, always<br>speculative | 1          | 0                   | 1            | 1               | most recently used flash word is<br>copied into second buffer line, next<br>flash word read is started; highest<br>performance for linear reads                    |  |  |

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

SJA2020 1

#### 8.1.2 Flash memory controller pin description

The flash memory controller has no external pins.

#### 8.1.3 Flash memory layout

The ARM processor can program the flash for ISP and IAP. Note that the flash always has to be programmed by flash words (of 128-bit).

The flash memory is organized in equal sectors of 8 kB that must be erased before data can be written into them. The flash memory also has sector wise protection. Writing occurs per page which consists of 4096 bits (32 flash words). Thus a sector contains 16 pages.

Table 9 and Table 10 give an overview of the flash sector and page addressing.

| Sector number | Sector base address |

|---------------|---------------------|

| 0             | 0000 0000h          |

| 1             | 0000 2000h          |

| 2             | 0000 4000h          |

| 3             | 0000 6000h          |

| 4             | 0000 8000h          |

| 5             | 0000 A000h          |

| 6             | 0000 C000h          |

| 7             | 0000 E000h          |

| 8             | 0001 0000h          |

| 9             | 0001 2000h          |

| 10            | 0001 4000h          |

| 11            | 0001 6000h          |

| 12            | 0001 8000h          |

| 13            | 0001 A000h          |

| 14            | 0001 C000h          |

| 15            | 0001 E000h          |

| 16            | 0002 0000h          |

| 17            | 0002 2000h          |

| 18            | 0002 4000h          |

| 19            | 0002 6000h          |

| 20            | 0002 8000h          |

| 21            | 0002 A000h          |

| 22            | 0002 C000h          |

| 23            | 0002 E000h          |

| 24            | 0003 0000h          |

| 25            | 0003 2000h          |

| 26            | 0003 4000h          |

| 27            | 0003 6000h          |

| 28            | 0003 8000h          |

|               |                     |

Table 9:

Flash sector overview

| Table 9:  | Flash sector overviewcontinued |                     |

|-----------|--------------------------------|---------------------|

| Sector nu | mber                           | Sector base address |

| 29        |                                | 0003 A000h          |

| 30        |                                | 0003 C000h          |

| 31        |                                | 0003 E000h          |

| 32        |                                | 0004 0000h          |

| 33        |                                | 0004 2000h          |

| 34        |                                | 0004 4000h          |

| 35        |                                | 0004 6000h          |

| 36        |                                | 0004 8000h          |

| 37        |                                | 0004 A000h          |

| 38        |                                | 0004 C000h          |

| 39        |                                | 0004 E000h          |

| 40        |                                | 0005 0000h          |

| 41        |                                | 0005 2000h          |

| 42        |                                | 0005 4000h          |

| 43        |                                | 0005 6000h          |

| 44        |                                | 0005 8000h          |

| 45        |                                | 0005 A000h          |

| 46        |                                | 0005 C000h          |

| 47        |                                | 0005 E000h          |

| 47        |                                | 0005 E000h          |

#### Table 10: Page addressing overview

| Page number | Page base address |

|-------------|-------------------|

| 0           | 0000 0000h        |

| 1           | 0000 0200h        |

| 2           | 0000 0400h        |

| 3           | 0000 0600h        |

| 4           | 0000 0800h        |

| 5           | 0000 0A00h        |

| 6           | 0000 0C00h        |

| 7           | 0000 0E00h        |

| 8           | 0000 1000h        |

| 9           | 0000 1200h        |

| 10          | 0000 1400h        |

| 11          | 0000 1600h        |

| 12          | 0000 1800h        |

| 13          | 0000 1A00h        |

| 14          | 0000 1C00h        |

| 15          | 0000 1E00h        |

The index sector is a special sector in which the JTAG access protection and sector security are located. The address space becomes visible by setting the FS\_ISS bit and overlaps the regular flash sectors address space.

Note that the index sector can not be erased and access to index sector has to be performed via code outside the flash.

#### 8.1.4 Register mapping

The flash memory controller registers are shown in <u>Table 11</u>. The flash memory controller registers have an offset to the base address FMC RegBase which can be found in the memory map (see Table 7).

|                   | Thas memory controller register summary |                |                |                                          |                     |

|-------------------|-----------------------------------------|----------------|----------------|------------------------------------------|---------------------|

| Address<br>offset | Туре                                    | Reset<br>value | Name           | Description                              | Reference           |

| 000h              | R/W                                     | 0005h          | FCTR           | flash control register                   | see Table 12        |

| 004h              | -                                       | -              | reserved       | reserved register; do not modify         |                     |

| 008h              | R/W                                     | 0000h          | FPTR           | flash program time register              | see Table 13        |

| 00Ch              | -                                       | -              | reserved       | reserved register; do not<br>modify      |                     |

| 010h              | R/W                                     | C004h          | FBWST          | flash bridge wait state<br>register      | see Table 14        |

| 014h              | -                                       | -              | reserved       | reserved register; do not modify         |                     |

| 018h              | -                                       | -              | reserved       | reserved register; do not modify         |                     |

| 01Ch              | R/W                                     | 000h           | FCRA           | flash clock divider register             | see Table 15        |

| 020h              | R/W                                     | 0000h          | FMSSTART       | flash BIST start address<br>register     | see Table 16        |

| 024h              | R/W                                     | 0 0000h        | FMSSTOP        | flash BIST stop address<br>register      | see Table 17        |

| 028h              | -                                       | -              | reserved       | reserved register; do not modify         |                     |

| 02Ch              | R                                       | -              | FMSW0          | flash 128-bit signature word 0 register  | see Table 18        |

| 030h              | R                                       | -              | FMSW1          | flash 128-bit signature word 1 register  | see Table 19        |

| 034h              | R                                       | -              | FMSW2          | flash 128-bit signature word 2 register  | see <u>Table 20</u> |

| 038h              | R                                       | -              | FMSW3          | flash 128-bit signature word 3 register  | see Table 21        |

| FD8h              | W                                       | -              | INT_CLR_ENABLE | flash clear interrupt enable register    | see Table 27        |

| FDCh              | W                                       | -              | INT_SET_ENABLE | flash set interrupt enable register      | see <u>Table 26</u> |

| FE0h              | R                                       | 0h             | INT_STATUS     | flash interrupt status register          | see Table 22        |

| FE4h              | R                                       | 0h             | INT_ENABLE     | flash interrupt enable register          | see Table 25        |

| FE8h              | W                                       | -              | INT_CLR_STATUS | flash clear interrupt status<br>register | see Table 24        |

| FECh              | W                                       | -              | INT_SET_STATUS | flash set interrupt status register      | see <u>Table 23</u> |

|                   |                                         |                |                |                                          |                     |

Table 11:

Flash memory controller register summary

#### 8.1.5 Flash control register (FCTR)

The flash control register is used to select read modes, and to control the programming of the flash memory.

The flash has data latches to store the data that is to be programmed into the flash. Instead of reading the flash contents, the data latch contents of the flash can be read. Data latch reading is always done without buffering, with the programmed number of wait states (WST) on every beat of the burst. Data latch reading can be done both synchronously and asynchronously. Data latch reading is selected with the FS\_RLD bit.

Index sector reading is always done without buffering, with the programmed number of wait states (WST) on every beat of the burst. Index sector reading can be done both synchronously and asynchronously. Index sector reading is selected with the FS\_ISS bit.

Table 12 shows the bit assignment of the FCTR register.

# Table 12. FCTR register bit description Legend: \* reset value \*

| Bit      | Symbol      | Access         | Value | Description                                                                                                                                                                                                               |

|----------|-------------|----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 to 16 | reserved    | -              | -     | reserved; do not modify, read as logic 0, write as logic 0                                                                                                                                                                |

| 15       | FS_LOADREQ  | R/W            |       | data load request                                                                                                                                                                                                         |

|          |             |                |       | the flash is written if FS_WRE has been set;<br>the data load is automatically triggered after<br>the last word was written to the load register;<br>this bit is automatically cleared and thus<br>always read as logic 0 |

|          |             |                | 0*    |                                                                                                                                                                                                                           |

| 14       | FS_CACHECLR | R/W            |       | buffer line clear                                                                                                                                                                                                         |

|          |             |                | 1     | all bits of the data transfer register are set                                                                                                                                                                            |

|          |             |                | 0*    |                                                                                                                                                                                                                           |

| 13       | FS_CACHEBYP | S_CACHEBYP R/W |       | buffering bypass                                                                                                                                                                                                          |

|          |             |                | 1     | reading from flash is without buffering                                                                                                                                                                                   |

|          |             |                | 0*    | the read buffering is active                                                                                                                                                                                              |

| 12       | FS_PROGREQ  | _PROGREQ R/W   |       | programming request                                                                                                                                                                                                       |

|          |             |                | 1     | flash programming is requested                                                                                                                                                                                            |

|          |             |                | 0*    |                                                                                                                                                                                                                           |

| 11       | FS_RLS      | S_RLS R/W      |       | select sector latches for reading                                                                                                                                                                                         |

|          |             |                | 1     | the sector latches are read                                                                                                                                                                                               |

|          |             |                | 0*    | the flash array is read                                                                                                                                                                                                   |

| 10       | FS_PDL      | R/W            |       | preset data latches                                                                                                                                                                                                       |

|          |             |                | 1     | all bits in the data latches are set                                                                                                                                                                                      |

|          |             |                | 0*    |                                                                                                                                                                                                                           |

| 9        | FS_PD       | R/W            |       | power down                                                                                                                                                                                                                |

|          |             |                | 1     | the flash is in power down                                                                                                                                                                                                |

|          |             |                | 0*    | the flash is not in power down                                                                                                                                                                                            |

| 8        | reserved    | -              | -     | reserved; do not modify, write as logic 0, read as logic 0                                                                                                                                                                |

SJA2020\_1

Objective data sheet

| Bit | Symbol   | Access    | Value                                    | Description                                                                        |

|-----|----------|-----------|------------------------------------------|------------------------------------------------------------------------------------|

| 7   | 7 FS_WPB | R/W       |                                          | program and erase protection                                                       |

|     |          |           | 1                                        | program and erase have been enabled                                                |

|     |          |           | 0*                                       | program and erase have been disabled                                               |

| 6   | FS_ISS   | R/W       |                                          | index sector selection                                                             |

|     |          |           | 1                                        | the index sector will be read                                                      |

|     |          |           | 0*                                       | the flash array will be read                                                       |

| 5   | FS_RLD   | R/W       |                                          | read data latches                                                                  |

|     |          |           | 1                                        | the data latches are read for verification of data that is loaded to be programmed |

|     |          |           | 0*                                       | the flash array is read                                                            |

| 4   | FS_DCR   | _DCR R/W  |                                          | DC read mode                                                                       |

|     |          |           | 1                                        | asynchronous reading has been selected                                             |

|     |          |           | 0*                                       | synchronous reading has been selected                                              |

| 3   | reserved | -         | -                                        | reserved; do not modify, write as logic 0, read<br>as logic 0                      |

| 2   | FS_WEB   | S_WEB R/W |                                          | program and erase enable                                                           |

|     |          |           | 1*                                       | program and erase have been disabled                                               |

|     |          |           | 0                                        | program and erase have been enabled                                                |

| 1   | FS_WRE   | R/W       |                                          | program and erase selection                                                        |

|     |          | 1         | program and data load have been selected |                                                                                    |

|     |          |           | 0*                                       | erase has been selected                                                            |

| 0   | FS_CS    | R/W       |                                          | flash chip select                                                                  |

|     |          |           | 1*                                       | the flash is active                                                                |

|     |          | 0         | the flash is in standby                  |                                                                                    |

# Table 12. FCTR register bit description ...continued

#### 8.1.6 Flash program time register (FPTR)

The flash program time register controls the timer for burning and erasing the flash memory. It also allows to read the remaining burn or erase time.

The erase time to be programmed can be calculated from the following formula:

$$TR = \frac{t_{er(sect)}}{512 \times t_{clk(sys)}}$$

The burn time to be programmed can be calculated from the following formula: